MOS 场效应晶体管

-

请简述 MOS 晶体管各个版图层的作用。

参考答案- 阱层:定义在衬底上制备阱的区域。NMOS 管制备在 P 型衬底上,PMOS 管制备在 N 型衬底上。一块原始的半导体材料,掺入的杂质类型只能有一种,即该衬底不是 N 型就是 P 型。如果不对衬底进行加工处理的话,该衬底只能制备一种 MOS 晶体管。CMOS 集成电路是把 NMOS 晶体管和 PMOS 晶体管制备在同一个��硅片衬底上,为了能够制造 CMOS 集成电路,需要对衬底进行处理,利用掺杂工艺在衬底上形成一个区域,该区域的掺杂类型和衬底的掺杂类型相反,这个区域就称为阱。

- 有源区层:在衬底上定义制作有源区的区域,该区域包括源区、漏区和沟道。在衬底上淀积厚氧化层,利用光刻和刻蚀工艺在衬底上开窗口并把厚氧化层除去就可形成有源区,有源区之外的区域是场区。显然,MOS 管必须而且只能制备在有源区内。

- 多晶硅层:定义制作多晶硅材料的区域。最早的 MOS 集成电路制造工艺只能制备一层多晶硅,而现在已经有能够制备两层多晶硅的工艺了。对于双层多晶硅工艺,第一层多晶硅主要用来制作栅极、导线和多晶硅-多晶硅电容的下极板,第二层多晶硅主要用来制作多晶硅电阻和多晶硅-多晶硅电容的上极板。双层多晶硅工艺具有多晶硅 1 和多晶硅 2 这两个版图层。

- P+ 注入层和 N+ 注入层:P+ 注入层定义注入 P+ 杂质离子的区域,而 N+ 注入层定义注入 N+ 杂质离子的区域。由于 NMOS 晶体管和 PMOS 晶体管的结构相同,只是源漏区的掺杂类型相反。同时,源区层只是定义了源区、漏区和沟道的区域,却没有说明源区和漏区的掺杂类型。P+ 注入层和 N+ 注入层说明了注入杂质的类型,也就是说明了有源区的导电类型,实现了 NMOS 晶体管和 PMOS 晶体管的区分。

- 接触孔层:定义制作接触孔的区域。MOS 晶体管的源极、漏极、栅极和衬底都要与电源或其它元件相连接,这样才能对 MOS 晶体管供使其工作并和其它元件一起组成具有使用价值的电路。有源区和场区的表面都有二氧化硅薄膜的存在,多晶硅栅极上也有二氧化硅薄膜,而二氧化硅不导电的,为了能对 MOS 晶体管的四个电极进行电连接,需要将衬底和多晶硅上某些区域上的二氧化硅去除,然后打开窗口,在窗口内填塞金属,用金属线进行连接。这些窗口就是接触孔,其作用是实现半导体材料和金属的欧姆接触,从而对 MOS 晶体管的各个电极进行电连接。

- 通孔层:定义制造通孔的区域。通孔和接触孔是不同的,接触孔是连接半导体和金属之间的窗口,而通孔是连接不同层金属之间的窗口。有的集成电路需要连接的节点和器件很多,一层金属难以满足布线要求,必须使用多层金属来进行布线连接,这就是多层金属互连。在多层金属互连系统中,通孔就是用来连接不同层金属的。

-

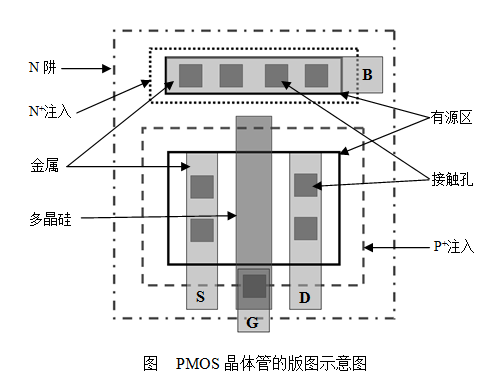

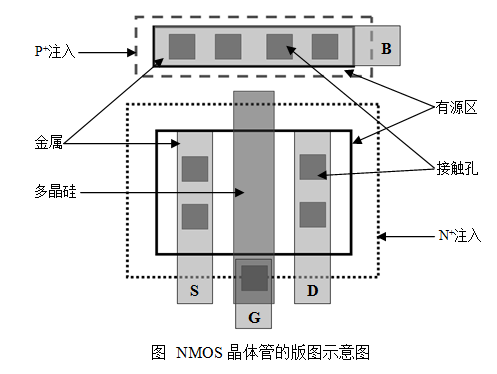

请画出 N 阱 CMOS 集成电路工艺下的 NMOS 晶体管和 PMOS 晶体管的版图示意图。

参考答案以 N 阱 CMOS 集成电路工艺为例,PMOS、NMOS 晶体管的版图如图所示。

-

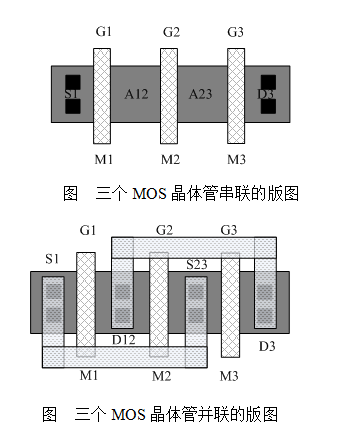

请画出三个 MOS 晶体管串联和并联的版图,考虑源漏共用技术。

参考答案

-

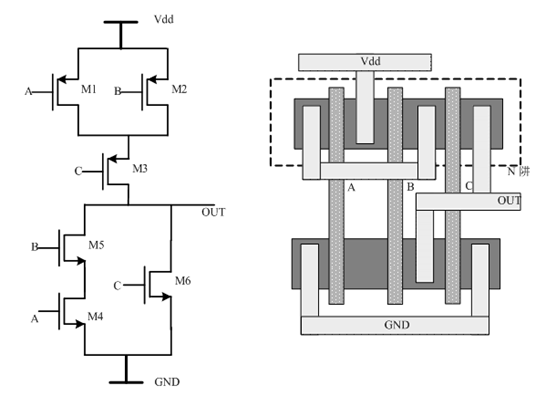

请画出数字集成电路中与或非门的电路图和版图。

参考答案

-

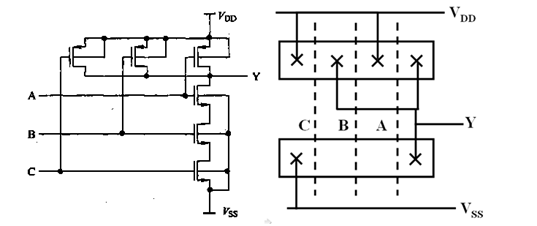

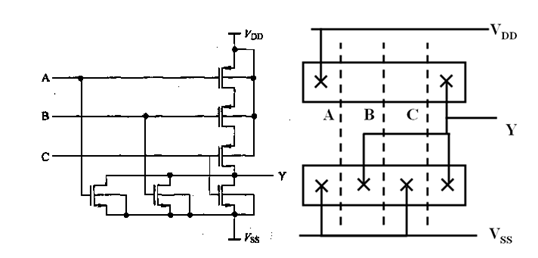

请画出三输入 CMOS 与非门和三输入 CMOS 或非门的电路图与棍棒图。

参考答案-

3 输入 CMOS 与非门的电路图与棍棒图:

-

3 输入 CMOS 非与门的电路图与棍棒图:

-

-

请简述宽长比特别大的 MOS 晶体管版图的处理方法。

参考答案- 步骤一:拆分。将宽长比很大的 MOS 晶体管的版图进行拆分,把它截成几段,拆分的数量以最终的版图接近方形为宜。

- 步骤二:源漏共用。对于拆分后的晶体管将它们并联。

- 步骤三:叉指连接。对版图进行金属连接。

-

特殊形状 MOS 晶体管的版图主要包括(曲线形状)、和(环形结构)两种。

-

MOS 晶体管的版图主要包括(直线型)、(曲线形)和(环形)等三种。

-

请简述天线效应及避免方法。

参考答案在 CMOS 集成电路制造工艺中,硅片处于零电位。在反应刻蚀进行过程中,2000 多伏的电压施加在中间的多晶硅材料上,随着多晶硅材料的不断被刻蚀,在留下的多晶硅材料上会积累电荷,如果多晶硅的体积比较大,就会积累大量的电荷,如果这些电荷产生的电场超过栅极氧化层的击穿场强,就会导致栅极氧化层损坏,MOS 晶体管在制造过程中就已经失效了。在反应离子刻蚀过程中,多晶硅材料像天线一样收集电荷,造成栅极氧化层击穿 MOS 晶体管失效的现象被称为天线效应。

天线效应和多晶硅栅极的面积成正比,因此将大面积的多晶硅分割成多个小面积的多晶硅并用金属进行连接可以保护处于刻蚀过程中的多晶硅材料。